# VHDL Logic Design Overview

EL 310 Erkay Savaş Sabancı University

## Combinational Logic

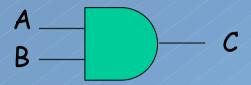

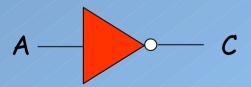

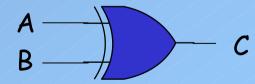

#### · Basic Gates

AND: C = AB

OR: C = A + B

NOT: C = A'

$XOR: C = A \oplus B$

### Truth Tables and Algebraic Expressions

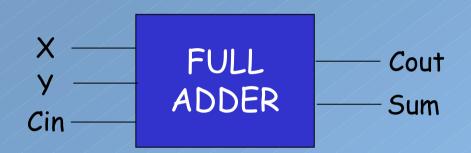

· Full Adder

| X | <b>/y</b> / | Cin | Cout | Sum |

|---|-------------|-----|------|-----|

| 0 | 0           | 0   | 0    | 0   |

| 0 | 0           | 1   | 0    | 1   |

| 0 | 1           | 0   | 0    | 1   |

| 0 | 1           | 1   | 1    | 0   |

| 1 | 0           | 0   | 0    | 1   |

| 1 | 0           | 1   | 1    | 0   |

| 1 | 1           | 0   | 1    | 0   |

| 1 | 1           | 1   | 1    | 1   |

### Minterm and Maxterm Expansions

#### Minterm expansion

Sum = X' Y' Cin + X' Y Cin' + X Y' Cin' + X Y Cin =

$$\sum$$

m(1, 2, 4, 7)

Cout = X' Y Cin + X Y' Cin + X Y Cin' + X Y Cin =  $\sum$  m(3, 5, 6, 7)

· Maxterm expansion

Sum =

$$(X+Y+Cin)(X+Y'+Cin')(X'+Y+Cin')(X'+Y'+Cin) = \prod M(0,3,5,6)$$

Cout =

$$(X+Y+Cin)(X+Y+Cin')(X+Y'+Cin)(X'+Y+Cin) = \prod M(0,1,2,4)$$

Minterm expansion Maxterm expansion

## Algebraic Simplification 1

- 1. Combining Terms (XY + XY'=X)-ABC'D' + ABCD' = ABD' (C + C') = ABD'

- Cout = X' Y Cin + X Y' Cin + X Y Cin' + X Y Cin = X' Y Cin + X Y' Cin + X Y Cin' + XY Cin + X Y Cin + X Y Cin = X' Y Cin + X Y Cin + X Y' Cin + X Y Cin + X Y Cin' + XY Cin = Y Cin + X Cin + XY

#### 2. Eliminating Terms

- -A'B + A'BC = A'B

- -Consensus theorem: XY + X'Z + YZ = XY + X'Z

### Algebraic Simplification 2

#### · Eliminating Literals

```

-X+X'Y=X+Y

```

```

- A'B + A'B'C'D' + ABCD' = A'(B + B'C'D') + ABCD'

= A'(B + C'D') + ABCD' = A'B + A'C'D' + ABCD'

= B (A' + ACD') + A'C'D'

= B (A' + CD') + A'C'D' = A'B + BCD' + A'C'D'

```

#### · Adding Redundant Terms

- Adding XX', multiplying by (X+X'),

- Adding YZ to XY + X'Z or adding XY to X

- AB + AD + A'C' + DB'C' = AB + DC'B' + AD + A'C' + DC' = AB + AD + A'C' + DC' = AB + AD + A'C'

# Duality Principle

· Important property of Boolean algebra

- If

$$x + 0 = x$$

then  $x \cdot 1 = x$

| x + x = x                  | $x \cdot x = x$                  |

|----------------------------|----------------------------------|

| x + x' = 1                 | $x \cdot x' = 0$                 |

| x + 1 = 1                  | $\times \cdot 0 = 0$             |

| $(x + y +)' = x' \cdot y'$ | $(x \cdot y \cdot)' = x' + y' +$ |

| $x + x \cdot y = x$        | $x \cdot (x+y) = x$              |

| xy + x'z + yz = xy + x'z   | (x+y)(x'+z)(y+z) = (x+y)(x'+z)   |

| (x+y)(x'+z) = x z + x' y   | xy + x'z = (x+z)(x'+y)           |

### Exclusive OR (XOR)

#### · Some rules

- X ⊕ 0 = X

- X ⊕ 1 = X'

- $-X \oplus X = 0$

- X ⊕ X' = 1

- Commutative, associative, and distributive laws hold.

- $X \oplus Y = X'Y + XY'$

- $(X \oplus Y)' = X \oplus Y' = X' \oplus Y = XY + X'Y'$

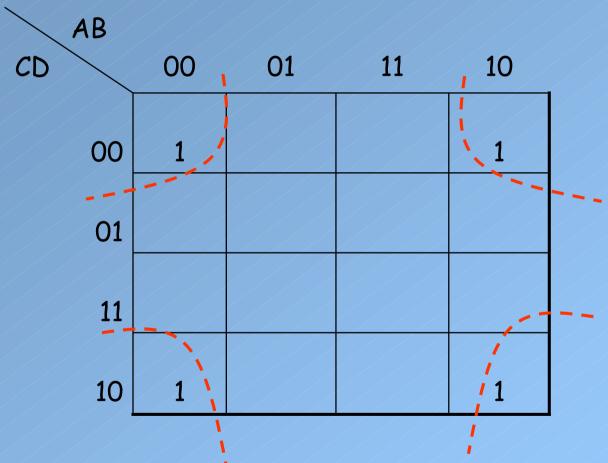

# Karnaugh Maps (1)

· F = A'B'C'D' + AB'C'D' + A'B'CD' + AB'CD'

• F = A'B'C'D' + AB'C'D' + A'B'CD' + AB'CD' = B'D'

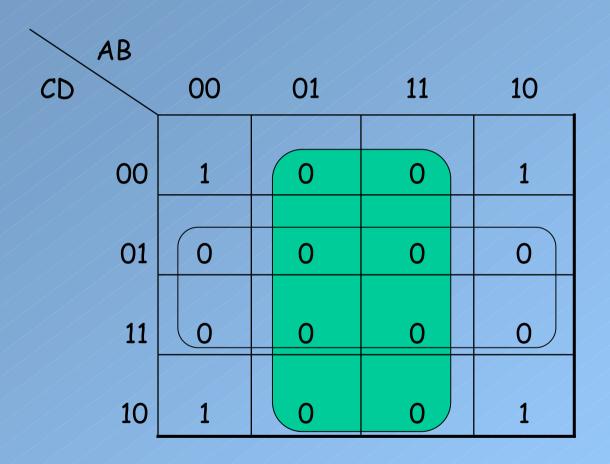

# Karnaugh Maps (2)

· F = A'B'C'D' + AB'C'D' + A'B'CD' + AB'CD'

F = (B+D)' = B'D' (DeMorgan's Law)

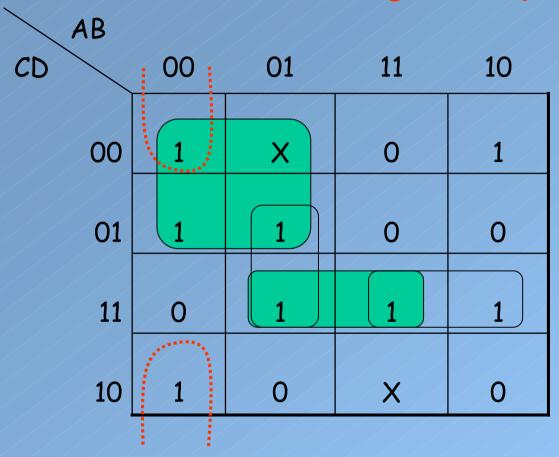

# Karnaugh Maps (3)

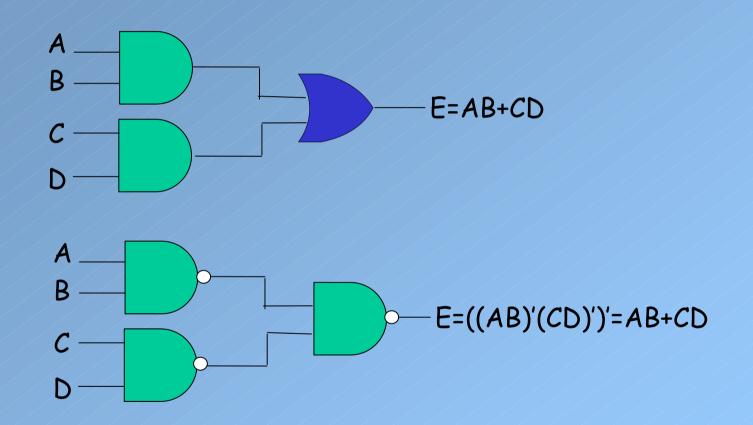

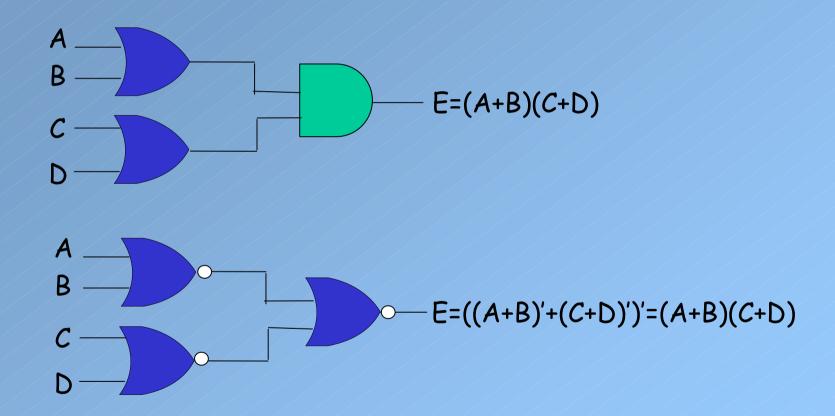

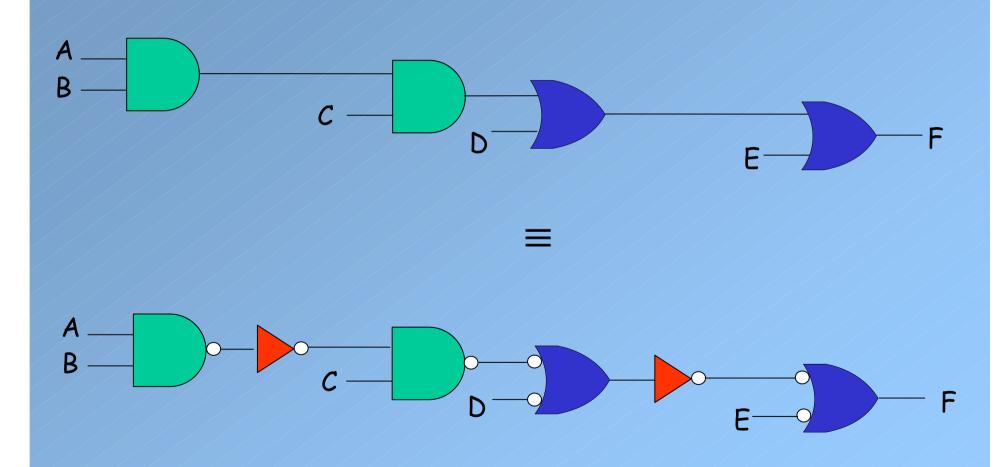

- In many technologies, implementation of NAND or NOR gates is easier than that of AND or OR gates

- Any logic function can be realized using only NAND gates or only NOR gates

NOR: C = (A+B)' = A'B'

· Conversion of AND-OR network to NAND gates

· Conversion of AND-OR Network to NOR gates

· Conversion of AND-OR network to NAND gates

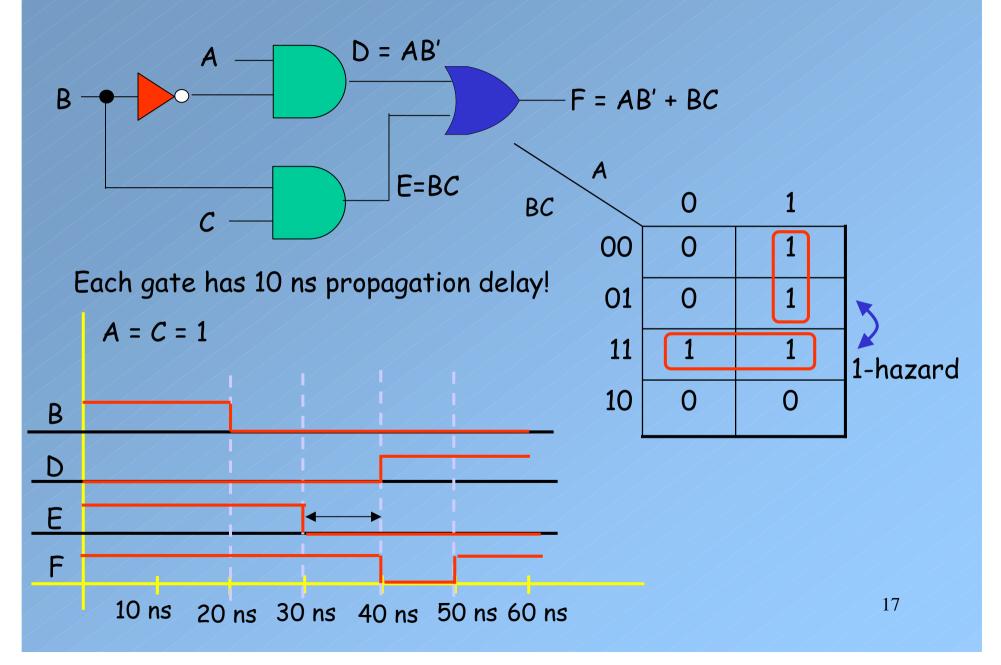

### Hazards in Combinational Networks - 1

- · Unwanted switching transients

- Occur when different paths from input to output have different propagation delays

- 1-hazard: network output may momentarily go to 0 when it should remain a constant 1

- 0-hazard: network output may momentarily go to 1 when it should remain a constant 0

- Dynamic-hazard: when the output is supposed to change (1-0 or 0-1), the output may change three times (e.g. 1-0-1-0)

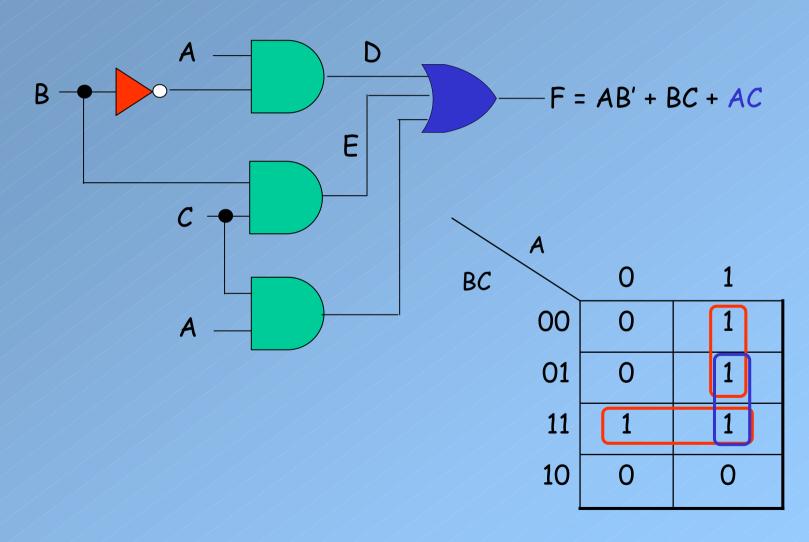

### Hazards in Combinational Networks -2

### Hazards in Combinational Networks -3

· Remedy

# Flip-Flops

#### D Flip-Flop

| D | Q | $Q^{\dagger}$ |

|---|---|---------------|

| 0 | 0 | 0             |

| 0 | 1 | 0             |

| 1 | 0 | 1             |

| 1 | 1 | 1             |

#### Clocked JK Flip-Flop

$$Q = JQ' + K'Q$$

| J | K | Ø | <del></del> |

|---|---|---|-------------|

| 0 | 0 | 0 | 0           |

| 0 | 0 | 1 | 1           |

| 0 | 1 | 0 | 0           |

| 0 | 1 | 1 | 0           |

| 1 | 0 | 0 | 1           |

| 1 | 0 | 1 | 1           |

| 1 | 1 | 0 | 1           |

| 1 | 1 | 1 | 0           |

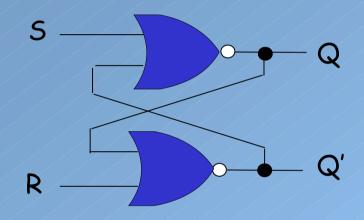

### Latches - 1

#### S-R Latch

| 5 | R | Q | Q <sup>+</sup> |

|---|---|---|----------------|

| 0 | 0 | 0 | 0              |

| 0 | 0 | 1 | 1              |

| 0 | 1 | 0 | 0              |

| 0 | 1 | 1 | 0              |

| 1 | 0 | 0 | 1              |

| 1 | 0 | 1 | 1              |

| 1 | 1 | 0 | -/-            |

| 1 | 1 | 1 |                |

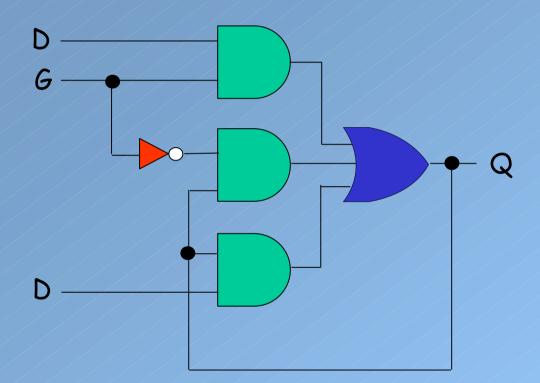

### Latches - 2

#### Gated D Latch

|   |   | _//_ |                |

|---|---|------|----------------|

| G | D | Ø    | Q <sup>†</sup> |

| 0 | 0 | 0    | 0              |

| 0 | 0 | 1    | 1              |

| 0 | 1 | 0    | 0              |

| 0 | 1 | 1    | 1              |

| 1 | 0 | 0/   | 0              |

| 1 | 0 | 1    | 0              |

| 1 | 1 | 0    | 1              |

| 1 | 1 | 1    | 1              |

$$Q^+ = DG + G'Q + DQ$$

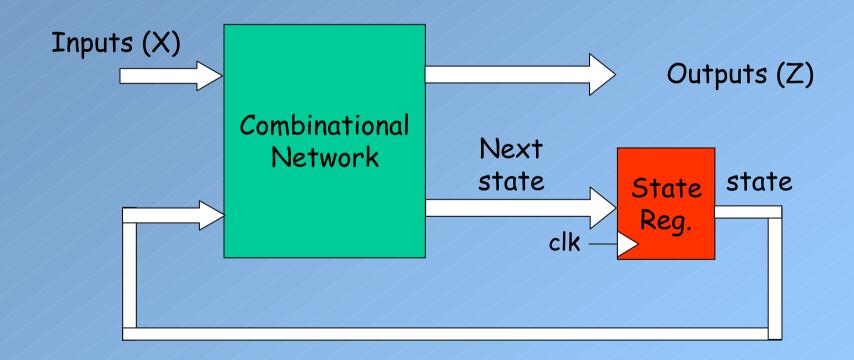

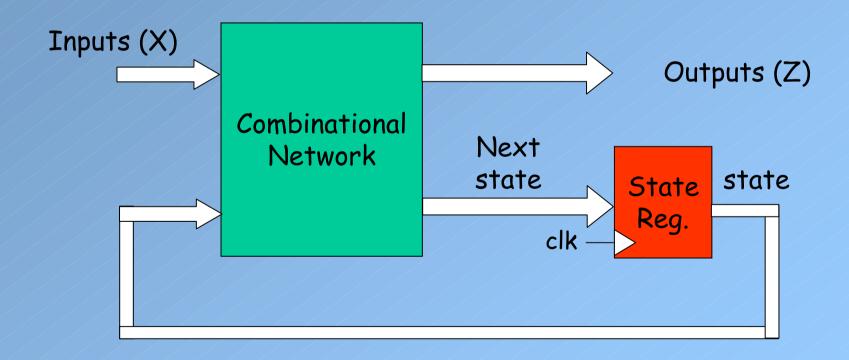

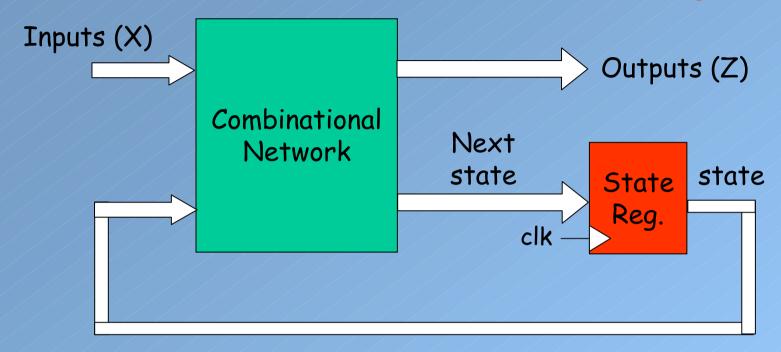

## Mealy Sequential Network Design

General Model of Mealy Sequential Design

Outputs depend on both present state and present input

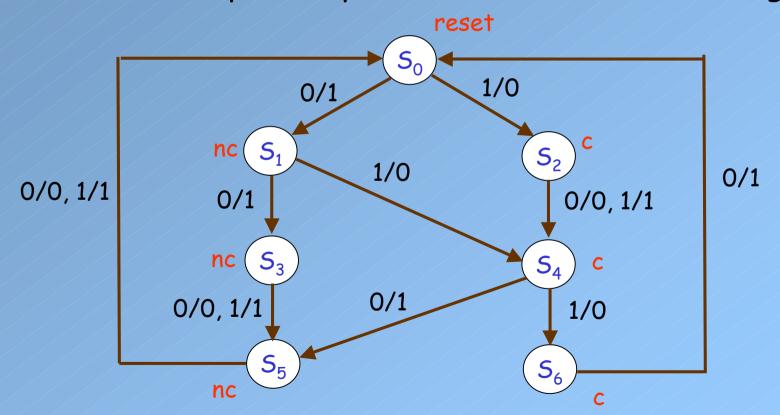

## Mealy Machine – Example (1)

- · Problem: code conversion

- Convert a BCD digit to another code by adding 3.

- For example,  $(1001)_2 + (0011)_2 = (1100)_2$

- Serial input/output, one bit at a time starting LSB.

## Mealy Machine – Example (2)

#### · State table

| Present               | Next State            |                       | Output  |          |

|-----------------------|-----------------------|-----------------------|---------|----------|

| State                 | input=0               | input=1               | input=0 | input=1  |

| <b>S</b> <sub>0</sub> | <b>S</b> <sub>1</sub> | 52                    | 1       | 0//      |

| S <sub>1</sub>        | <b>S</b> <sub>3</sub> | <b>S</b> <sub>4</sub> | 1       | 0/       |

| <b>S</b> <sub>2</sub> | <b>S</b> <sub>4</sub> | <b>S</b> <sub>4</sub> | 0//     | 1        |

| <b>S</b> <sub>3</sub> | S <sub>5</sub>        | S <sub>5</sub>        | 0       | 1        |

| S <sub>4</sub>        | S <sub>5</sub>        | <b>S</b> <sub>6</sub> | 1       | 0/       |

| S <sub>5</sub>        | <b>S</b> <sub>0</sub> | <b>S</b> <sub>0</sub> | 0       | 1        |

| <b>S</b> <sub>6</sub> | <b>S</b> <sub>0</sub> |                       | 1       | <u> </u> |

- Seven states → three flip-flops

- <u>Challenge</u>: state assignment to FF so that logic is the simplest

## Mealy Machine – Example (3)

· State Assignments

| $Q_1$    |                       |                       |

|----------|-----------------------|-----------------------|

| $Q_2Q_3$ | 0                     | 1                     |

| 00       | <b>5</b> <sub>0</sub> | 51                    |

| 01       | 0                     | 52                    |

| 11       | S <sub>5</sub>        | <b>5</b> <sub>3</sub> |

| 10       | 56                    | 54                    |

Assignment map

|          |       | $Q_1^+ Q_2^+ Q_3^+$ |     | Z   |     |

|----------|-------|---------------------|-----|-----|-----|

| $Q_1Q_2$ | $Q_3$ | X=0                 | X=1 | X=0 | X=1 |

| 00       | 0//   | 100                 | 101 | 1   | 0   |

| 10       | 0     | 111                 | 110 | 1   | 0/  |

| 10       | 1     | 110                 | 110 | 0// | 1   |

| 11       | 1     | 011                 | 011 | 0   | 1   |

| 110      | 0     | 011                 | 010 | 1   | 0   |

| 01       | 1     | 000                 | 000 | 0   | 1   |

| 01       | 0//   | 000                 | xxx | 1   | X   |

| 00       | 1     | xxx                 | xxx | X   | X   |

Transition Table

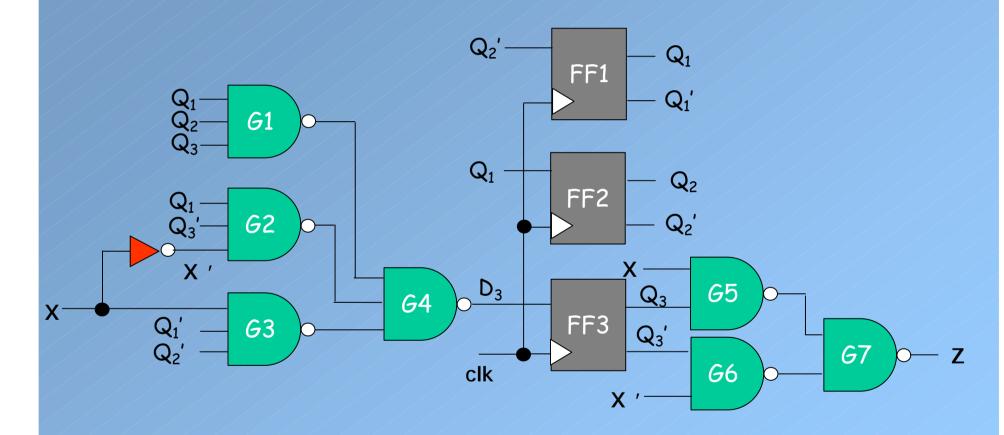

# Mealy Machine – Example (4)

· Realization of Code Converter

### Moore Machine

- The output is only function of the present state, independent of the input.

- · Input determines the next state.

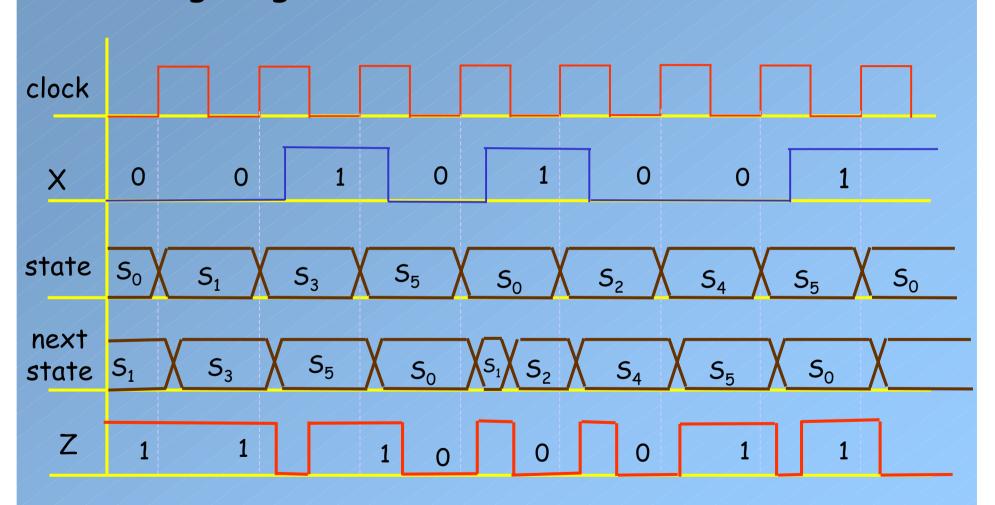

## Sequential Network Timing

· Timing diagram for Code Converter

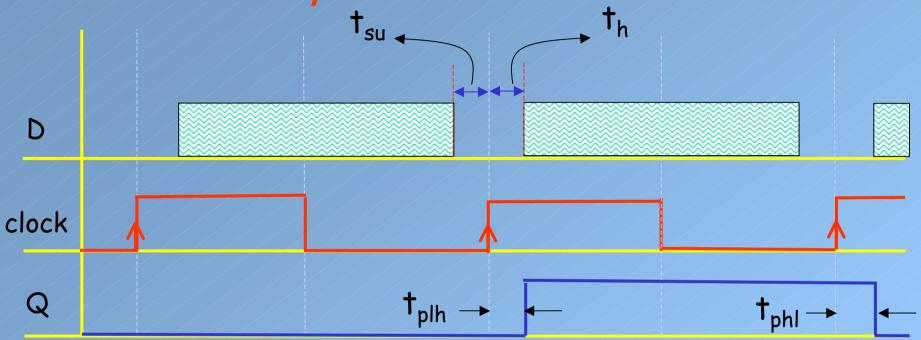

### Setup and Hold Times 1

#### · For an ideal D flip-flop

- If the D input changes at exactly the same time as the active edge of the clock, flip-flop operate correctly

#### In reality

- The D input must be stable for a certain amount of time before the active edge of the clock; <u>setup</u> <u>time</u>

- Furthermore, D must be stable for a certain amount of time after the active edge of the clock; <u>hold</u> <u>time</u>

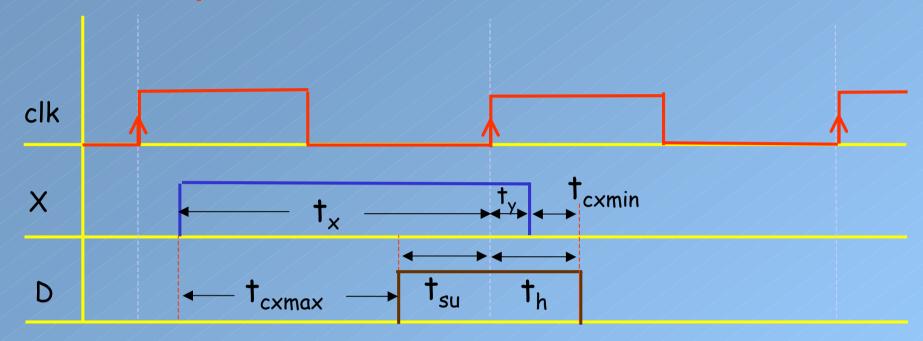

## Setup and Hold Times 2

- · In shaded interval above D may be changed

- Otherwise, it cannot be determined whether the flipflop will change state

- Even worse, the flip-flop may malfunction and output a short pulse and even go into oscillation

## Maximum Clock Frequency

- t<sub>ck</sub>: clock period; t<sub>pmax</sub> = max(t<sub>plh</sub>, t<sub>phl</sub>)

- t<sub>cmax</sub>: maximum propagation delay through combinational network

- Then,  $t_{pmax} + t_{cmax} \le t_{ck} t_{su}$ .

### Setup and Hold-time Violations (1)

- · Hold-time violation

- If the change in Q fed back through the combinational network and caused D to change too soon after the clock edge.

- t<sub>pmin</sub> + t<sub>cmin</sub> ≥ t<sub>h</sub> (t<sub>pmin</sub> > t<sub>h</sub> for normal flip-flops)

- Usually, setup or hold-time violation occurs if the input X to the network changes too close to the active edge of the clock.

- We must make sure that an input change propagates to the flip-flop inputs such that setup time is satisfied before the active edge of the clock.

## Setup and Hold-time Violations (2)

- · For setup time: t<sub>x</sub> ≥ t<sub>cxmax</sub> + t<sub>su</sub>

- For hold-time:  $t_y \ge t_h t_{cxmin}$  or  $(t_y + t_{cxmin} \ge t_h)$

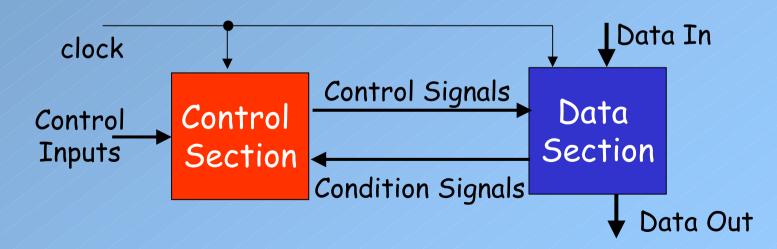

## Synchronous Design

- A clock is used

- To synchronize the operation of all flip-flops, registers, and counters in the system

- All state changes occur following the active edge of the clock

- The clock period must be long enough so that all flip-flop and register inputs will have time to stabilize before the next active edge of the clock

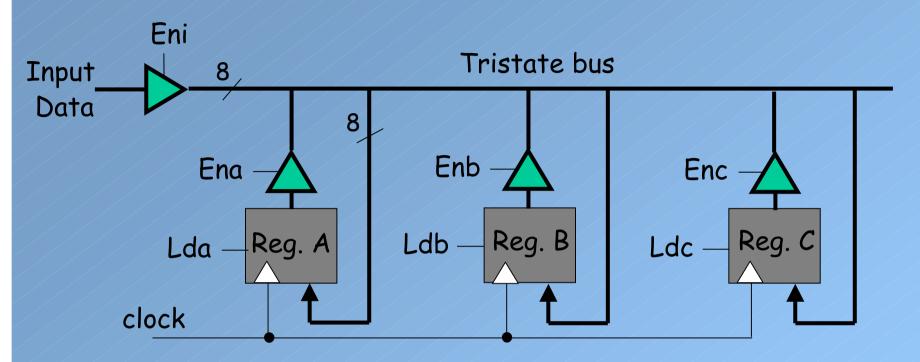

### Tristate Logic and Buses

Tristate buffers

- · Hi-Z: high-impedance which is equivalent to an open circuit.

- We use tristate buffers to connect the outputs of more than one gates or flip-flops.

### Tristate Bus

- If Enb = Ldc = 1 (all others 0), then the data in register B will be copied into register C when the active edge of the clock occurs.

- If Eni = Lda = Ldc = 1 then the input data will be loaded in registers A and C when the registers are clocked.